## EE 435

### Lecture 22

**Offset Voltages**

Review from last lecture

## **Offset Voltage**

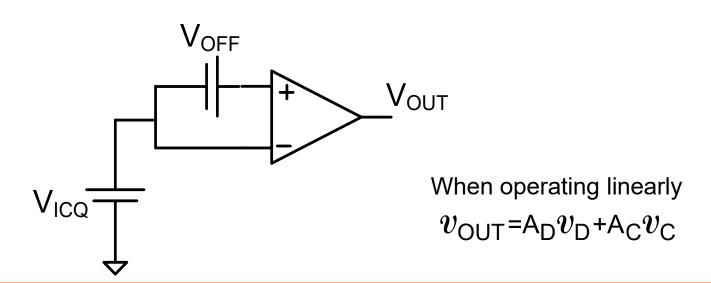

Definition: The input-referred offset voltage is the differential dc input voltage that must be applied to obtain the desired output when  $V_{ic}$  is the quiescent common-mode input voltage.

$V_{OFF}$  is usually related to the output offset voltage by the expression

$$V_{OFF} = \frac{V_{OUTOFF}}{A_D}$$

$V_{OFF}$  is dependent upon  $V_{ICQ}$  although this dependence is usually quite weak and often not specified

V<sub>OFF</sub> almost always large enough to force op amp out of linear mode for good op amps if used open loop

Review from last lecture Offset Voltage

Two types of offset voltage:

- Systematic Offset Voltage

- Random Offset Voltage

After fabrication it is impossible (difficult) to distinguish between the systematic offset and the random offset in any individual op amp

Measurements of offset voltages for a large number of devices will provide mechanism for identifying systematic offset and statistical characteristics of the random offset voltage

## Gradient and Local Random Effect

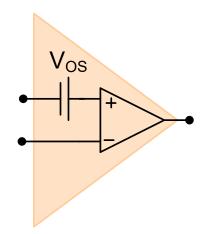

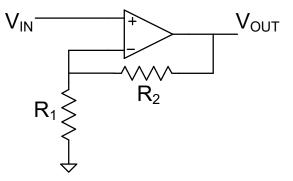

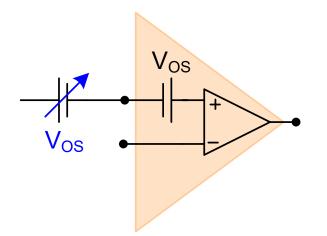

Can be modeled as a dc voltage source in series with the input

Effects of Offset Voltage - an example

Desired I/O relationship

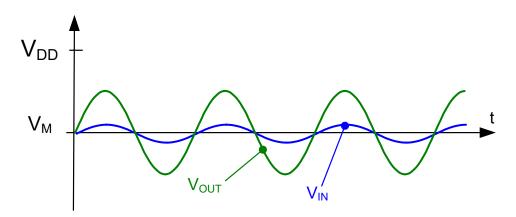

Effects of Offset Voltage - <u>an example</u>

By Superposition:

$$\mathbf{V}_{\text{OUT}} = \left(1 + \frac{\mathbf{R}_2}{\mathbf{R}_1}\right) \mathbf{V}_{\text{IN}} + \left(1 + \frac{\mathbf{R}_2}{\mathbf{R}_1}\right) \mathbf{V}_{\text{OS}}$$

In this feedback circuit,  $V_{OS}$  multiplied by same gain as  $V_{IN}$

Particularly problematic if V<sub>IN</sub> is small (so FB gain is then usually large)

Effects can be reduced or eliminated by adding equal amplitude opposite DC signal (many ways to do this)

Widely used in offset-critical applications

Comes at considerable effort and expense for low offset

#### Prefer to have designer make $V_{OS}$ small in the first place

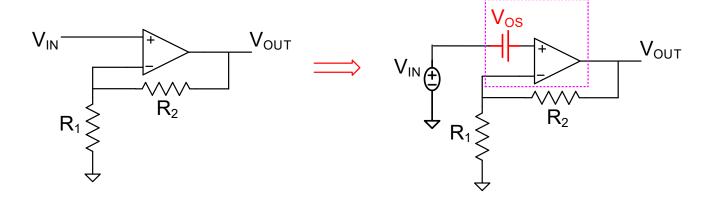

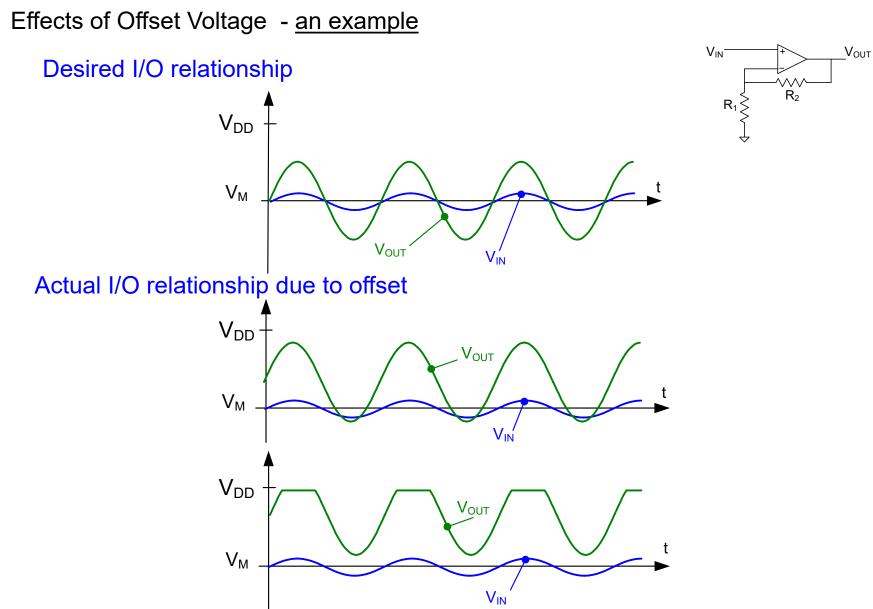

# Effects of Offset Voltage

- Deviations in performance will change from one instantiation to another due to the random component of the offset

- Particularly problematic in circuits with high FB gain

- A major problem in many other applications

- Not of concern in many applications as well

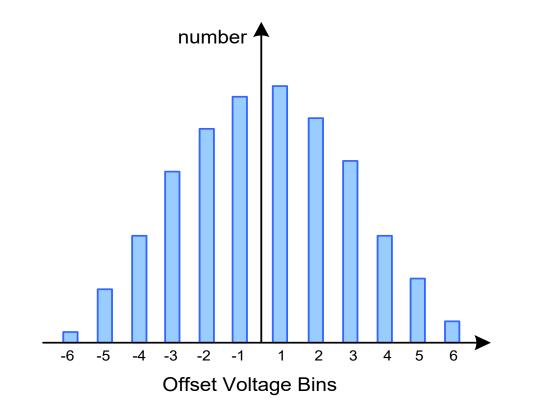

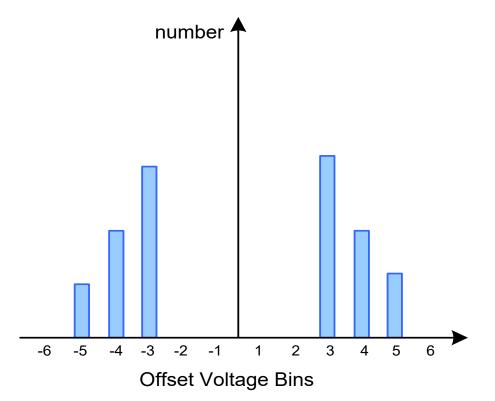

Typical histogram of random offset voltage (binned) after fabrication

Typical histogram of offset voltage (binned) after fabrication Mean is nearly 0 (mean is actually the systematic offset voltage)

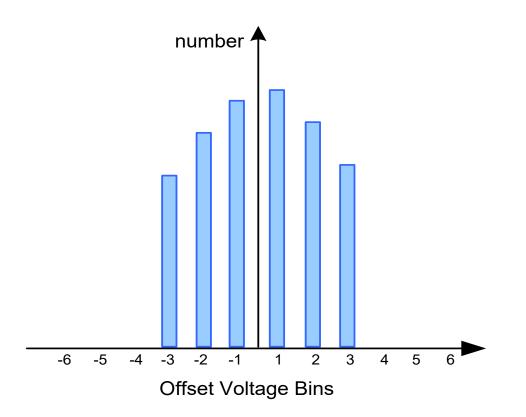

Typical histogram of offset voltage (binned) in shipped parts

Extreme offset parts have been sifted at test

Typical histogram of offset voltage (binned) in shipped parts

Low-offset parts sometimes sold at a premium

Extreme offset parts have been sifted at test

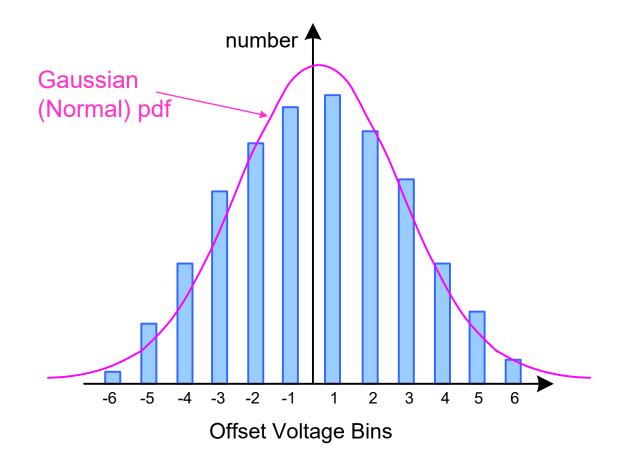

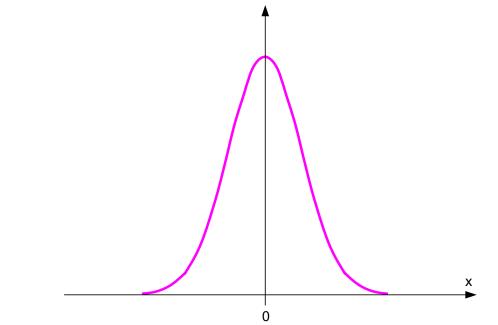

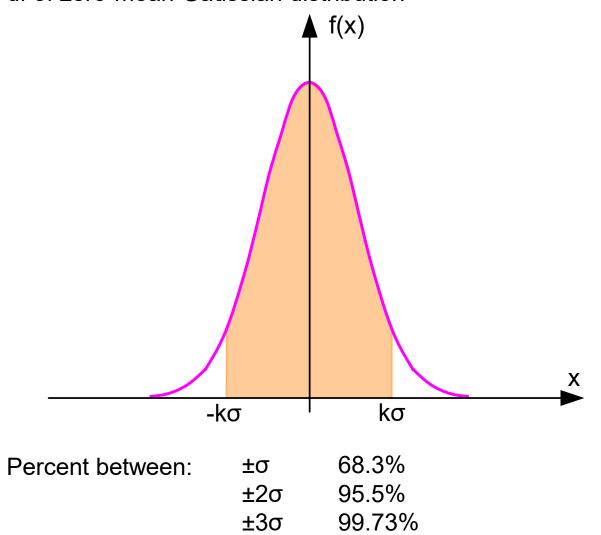

Pdf of zero-mean Gaussian distribution

Characterized by its standard deviation  $\sigma$  or variance  $\sigma^2$

Offset voltage often specified as the  $1\sigma$  or  $3\sigma$  value (though authors may neglect to indicate which)

For catalog parts, often specified as the worst-case value after sorted

Pdf of zero-mean Gaussian distribution

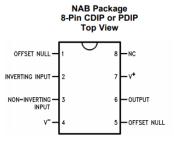

#### TL082-N

www.ti.com

SNOSBW5C - APRIL 1998 - REVISED APRIL 2013

#### TL082 Wide Bandwidth Dual JFET Input Operational Amplifier

Check for Samples: TL082-N

#### FEATURES

- Internally Trimmed Offset Voltage: 15 mV

- Low Input Bias Current: 50 pA

- Low Input Noise Voltage: 16nV/√Hz

- Low Input Noise Current: 0.01 pA/√Hz

- Wide Gain Bandwidth: 4 MHz

- High Slew Rate: 13 V/µs

- Low Supply Current: 3.6 mA

- High Input Impedance: 10<sup>12</sup>Ω

- Low Total Harmonic Distortion: ≤0.02%

- Low 1/f Noise Corner: 50 Hz

- Fast Settling Time to 0.01%: 2 μs

**₽**m

#### DESCRIPTION

These devices are low cost, high speed, dual JFET input operational amplifiers with an internally trimmed input offset voltage (BI-FET II<sup>™</sup> technology). They require low supply current yet maintain a large gain bandwidth product and fast slew rate. In addition, well matched high voltage JFET input devices provide very low input bias and offset currents. The TL082 is pin compatible with the standard LM1558 allowing designers to immediately upgrade the overall performance of existing LM1558 and most LM358 designs.

These amplifiers may be used in applications such as high speed integrators, fast D/A converters, sample and hold circuits and many other circuits requiring low

#### www.ti.com

SNOSBW5C-APRIL 1998-REVISED APRIL 2013

#### DC Electrical Characteristics (1)

| Symbol Parameter    | Conditions                                    |                                                                          | Unite                                                     |                                                                                  |                                                                                                          |

|---------------------|-----------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

|                     | Conditions                                    | Min                                                                      | Тур                                                       | Max                                                                              | Units                                                                                                    |

| nput Offset Voltage | R <sub>S</sub> = 10 kΩ, T <sub>A</sub> = 25°C |                                                                          | 5                                                         | 15                                                                               | m∨                                                                                                       |

|                     | Over Temperature                              |                                                                          |                                                           | 20                                                                               | m∨                                                                                                       |

| r                   |                                               | nput Offset Voltage $R_S = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$ | pput Offset Voltage $R_S = 10 k\Omega, T_A = 25^{\circ}C$ | MinTypnput Offset Voltage $R_S = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$ 5 | ParameterConditionsMinTypMaxnput Offset Voltage $R_S = 10 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$ 515 |

#### Sifted at test if |V<sub>OFF</sub>|>15mV

Guess 3o value of trimmed but non-culled population is 15 mV

#### LM741

SNOSC25D - MAY 1998 - REVISED OCTOBER 2015

#### LM741 Operational Amplifier

#### 1 Features

- · Overload Protection on the Input and Output

- No Latch-Up When the Common-Mode Range is Exceeded

#### 3 Description

The LM741 series are general-purpose operational amplifiers which feature improved performance over industry standards like the LM709. They are direct, plug-in replacements for the 709C, LM201, MC1439, and 748 in most applications.

#### 2 Annlicatione

www.ti.com

LM741

SNOSC25D - MAY 1998 - REVISED OCTOBER 2015

#### 6.5 Electrical Characteristics, LM741<sup>(1)</sup>

| PARAMETER                                | TEST CO                             | MIN                             | ТҮР | MAX | UNIT |    |

|------------------------------------------|-------------------------------------|---------------------------------|-----|-----|------|----|

| Input offset voltage                     | B < 10 k0                           | T <sub>A</sub> = 25°C           |     | 1   | 5    | mV |

|                                          | R <sub>S</sub> ≤ 10 kΩ              | $T_{AMIN} \le T_A \le T_{AMAX}$ |     |     | 6    | mV |

| Input offset voltage<br>adjustment range | $T_A = 25^{\circ}C, V_S = \pm 20 V$ |                                 |     | ±15 |      | mV |

|                                          |                                     |                                 |     |     |      |    |

www.fairchildsemi.com

### LM741 Single Operational Amplifier

#### Features

- · Short circuit protection

- · Excellent temperature stability

- · Internal frequency compensation

- High Input voltage range

- Null of offset

#### Description

The LM741 series are general purpose operational amplifiers. It is intended for a wide range of analog applications. The high gain and wide range of operating voltage provide superior performance in intergrator, summing amplifier, and general feedback applications.

- ---

#### **Electrical Characteristics**

(V<sub>CC</sub> = 15V, V<sub>EE</sub> = - 15V. T<sub>A</sub> =  $25 \circ$ C, unless otherwise specified)

| Parameter                                | Symbol | Conditions             | LM7  | Unit |      |      |  |

|------------------------------------------|--------|------------------------|------|------|------|------|--|

| Falameter                                | Symbol | conditions             | Min. | Тур. | Max. | onic |  |

| Input Offset Voltage                     | Vio    | Rs≤10KΩ                | -    | 2.0  | 6.0  | mV   |  |

|                                          | VIO    | Rs≤50Ω                 | -    | -    | -    | шv   |  |

| Input Offset Voltage<br>Adjustment Range | VIO(R) | V <sub>CC</sub> = ±20V | -    | ±15  | -    | mV   |  |

| Input Offset Current                     | lio    | -                      | -    | 20   | 200  | nA   |  |

| Input Bias Current                       | IBIAS  | -                      | -    | 80   | 500  | nA   |  |

#### LM741 Operational Amplifier

#### **General Description**

The LM741 series are general purpose operational amplifiers which feature improved performance over industry standards like the LM709. They are direct, plug-in replacements for the 709C, LM201, MC1439 and 748 in most applications.

The amplifiers offer many features which make their application nearly foolproof: overload protection on the input and output, no latch-up when the cc ceeded, as well as freedom from The LM741C/LM741E are identi except that the LM741C/LM741 guaranteed over a 0°C to +70 stead of -55°C to +125°C.

November 1994

| Parameter                             | Conditions                                                                                                                       | LM7 | LM741A/LM741E |     | LM741 |     | LM741C |     |     | Units |          |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|---------------|-----|-------|-----|--------|-----|-----|-------|----------|

|                                       |                                                                                                                                  | Min | Тур           | Max | Min   | Тур | Max    | Min | Тур | Max   | Units    |

| Input Offset Voltage                  | $\begin{array}{l} T_{A}=25^{\circ}C\\ R_{S}\leq10\ k\Omega\\ R_{S}\leq50\Omega \end{array}$                                      |     | 0.8           | 3.0 |       | 1.0 | 5.0    |     | 2.0 | 6.0   | mV<br>mV |

|                                       | $\label{eq:tampa} \begin{split} T_{AMIN} &\leq T_A \leq T_{AMAX} \\ R_S &\leq 50 \Omega \\ R_S &\leq 10 \; k \Omega \end{split}$ |     |               | 4.0 |       |     | 6.0    |     |     | 7.5   | mV<br>mV |

| Average Input Offset<br>Voltage Drift |                                                                                                                                  |     |               | 15  |       |     |        |     |     |       | μV/°C    |

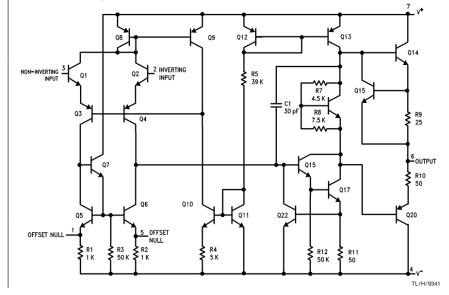

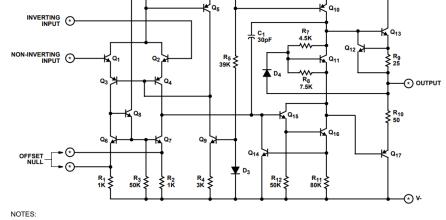

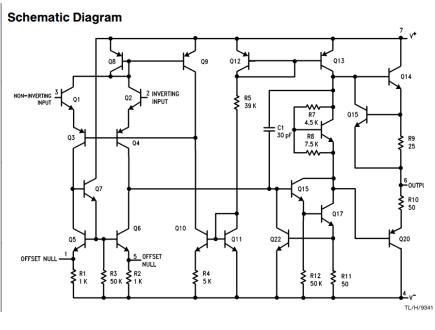

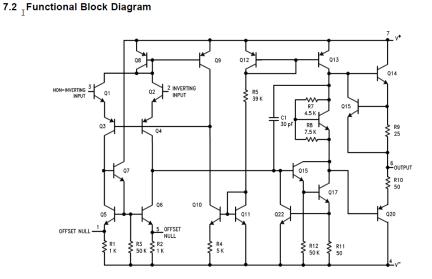

Schematic Diagram (Notes 5, 6)

#### **Schematic Diagram**

CA741C, CA741, LM741C, LM741 AND FOR EACH AMPLIFIER OF THE CA1458, CA1558, AND LM1458

National

Intersil

National

**Texas Instruments**

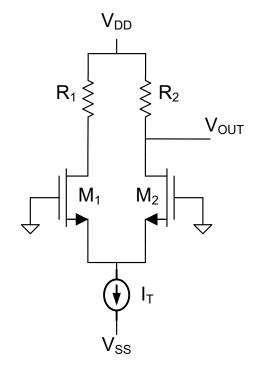

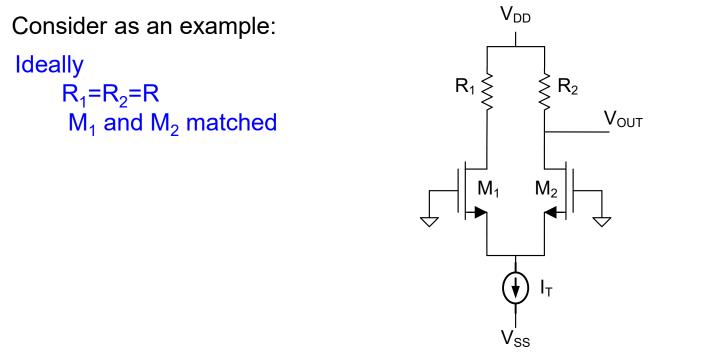

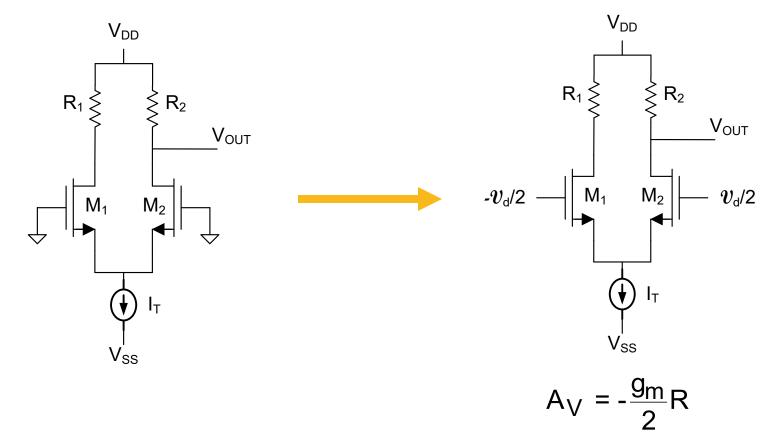

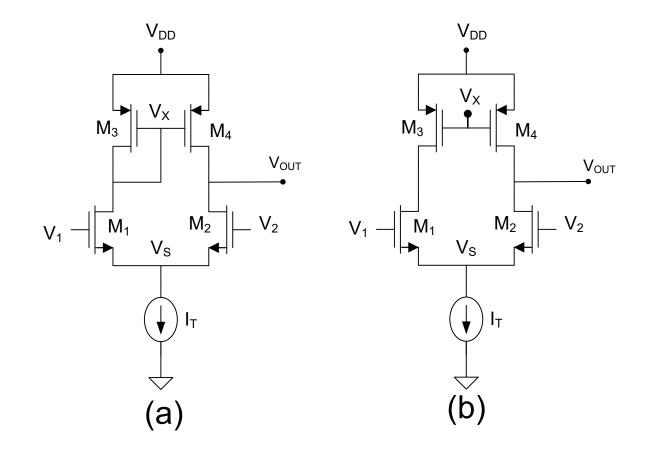

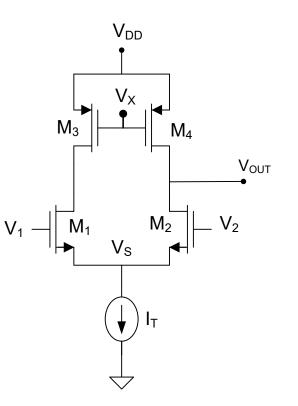

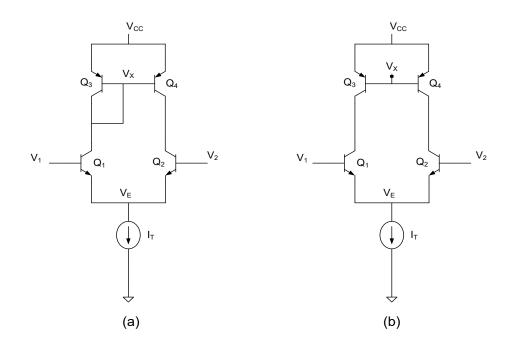

Consider as an example:

Ideally  $R_1 = R_2 = R$ ,  $M_1$  and  $M_2$  are matched

$$V_{OUT} = V_{DD} - \left(\frac{I_T}{2}\right)R$$

Assume this is the desired output voltage

If everything ideal except  $R_2 = R + \Delta R$  (actually there will be mismatches between  $M_1$  and  $M_2$  also)

$$V_{OUT} = V_{DD} - \left(\frac{I_T}{2}\right) [R + \Delta R]$$

$$\Delta V_{OUT} = - \left(\frac{I_T}{2}\right) \Delta R$$

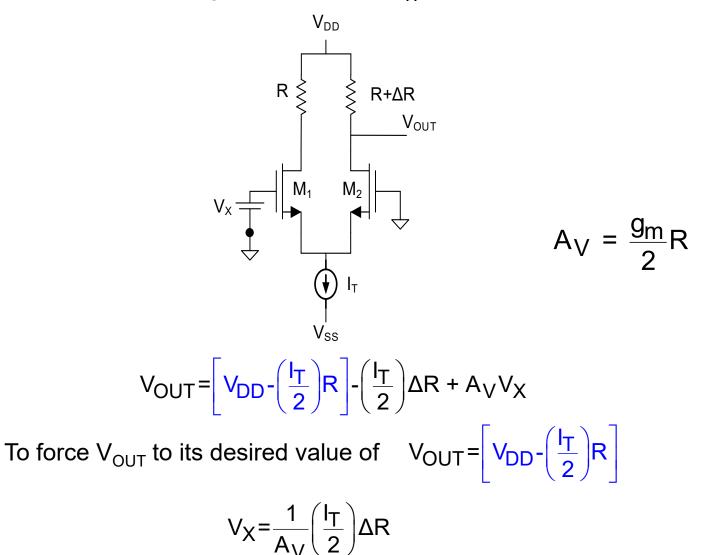

Consider as an example:

Determine the offset voltage -i.e. value of V<sub>x</sub> needed to obtain desired output

Determine the offset voltage – i.e. value of  $V_X$  needed to obtain desired output

Determine the offset voltage – i.e. value of  $V_X$  needed to obtain desired output

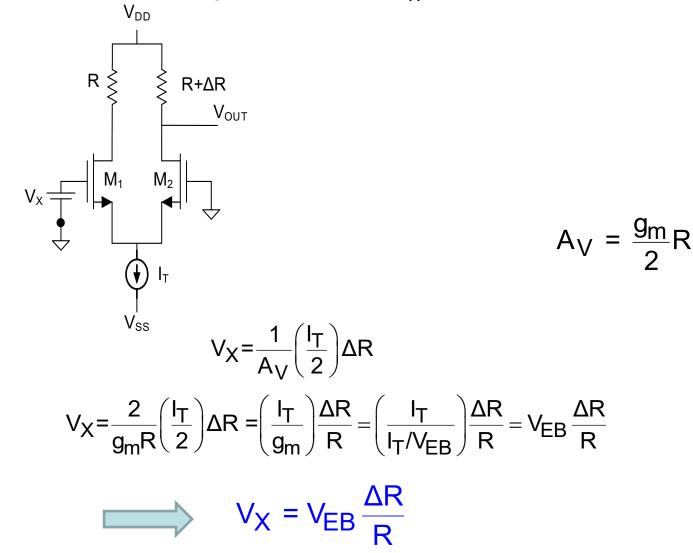

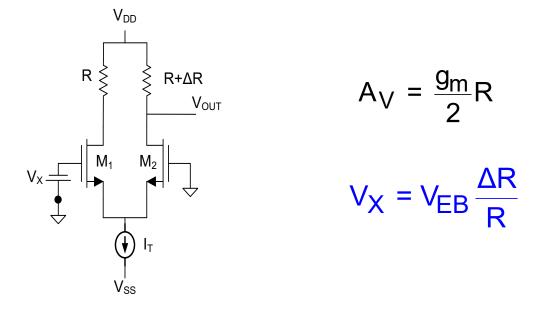

What can the designer do to reduce the offset voltage if the resistor value and statistics are fixed?

#### Reduce $V_{EB}$

Will that affect the voltage gain?

$$A_{V} = \frac{g_{m}}{2}R = \frac{2\frac{I_{T}}{2V_{EB}}}{2}R = \frac{1}{2V_{EB}}I_{T}R$$

Not if  $I_T$  is reduced by the same amount but that will affect signal swing and GB

The random offset voltage is almost entirely that of the input stage in most op amps

- Due to random variations in process parameters and device dimensions

- Random offset is actually a random variable at the design level but deterministic after fabrication in any specific device

- Distribution naturally nearly Gaussian (could be un-naturally manipulated)

Has zero mean

Characterized by its standard deviation or variance

Often strongly layout dependent

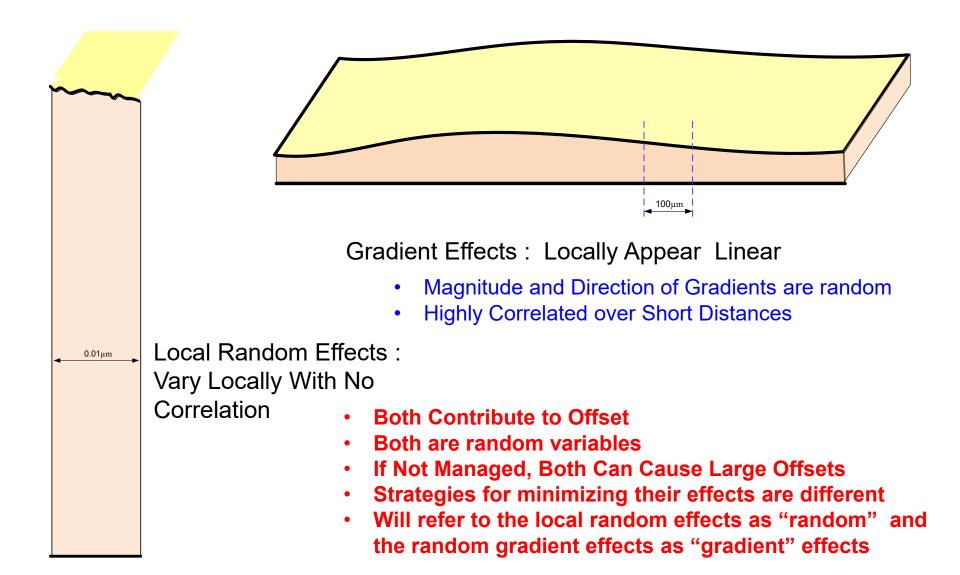

Due to both local random variations and correlated gradient effects

- Will consider both effects separately

- o Gradient effects usually dominate if not managed

- Good methods exist for driving gradient effects to small levels

Notation: Henceforth, the term "Random Offset" will refer to that due to local random variations and gradient effects will be considered separately

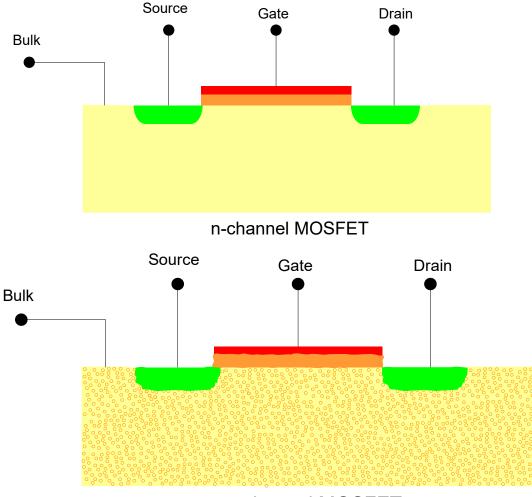

### Offset Voltages due to Local Random Variations

n-channel MOSFET

Impurities vary randomly with position as do edges of gate, oxide and diffusions

Model and design parameters vary throughout channel and thus the corresponding equivalent lumped model parameters will vary from device to device

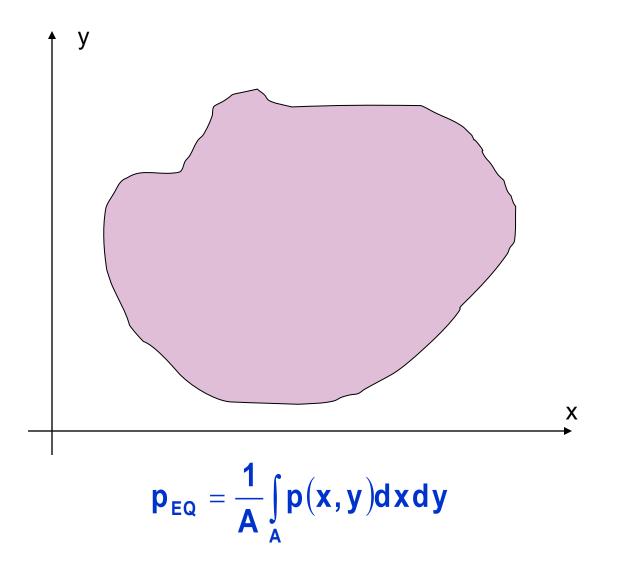

# **Model Parameter Variation**

Define p to be a process parameter that varies with lateral position throughout the region defined by the channel of the transistor.

Almost Theorem:

If p(x,y) varies throughout a two-dimensional region, then

$$\mathbf{p}_{EQ} = \frac{1}{A} \int_{A} \mathbf{p}(\mathbf{x}, \mathbf{y}) d\mathbf{x} d\mathbf{y}$$

Parameters such at  $V_{T}\!$ ,  $\mu$  and  $C_{OX}$  vary throughout a two-dimensional region

Local random variations introduce a random component in device model parameters which are uncorrelated but for ideally matched devices they are identically distributed

$$e.g. \quad V_{\text{TEQi}} = V_{\text{TN}} + V_{\text{TR}\,i}$$

$V_{TRi}$  and  $V_{TRj}$  due to local random variations are uncorrelated for i $\neq$ j but if ideally matched they are identically distributed

## **Model Parameter Variation**

The random offset associated with <u>local random variations</u> is due to mismatches in the four transistors, dominantly mismatches in the parameters { $V_T$ ,  $\mu$ ,  $C_{OX}$ , W and L}

The relative mismatch effects become more pronounced as devices become smaller

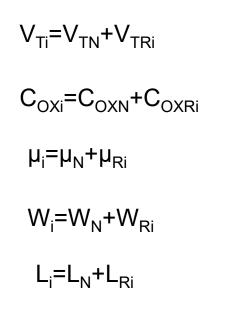

$V_{Ti} = V_{TN} + V_{TRi}$   $C_{OXi} = C_{OXN} + C_{OXRi}$   $\mu_i = \mu_N + \mu_{Ri}$   $W_i = W_N + W_{Ri}$   $L_i = L_N + L_{Ri}$

Each design and model parameter is comprised of a nominal part and a random component

It will be assumed that the random parts of each model parameter are uncorrelated but if ideally matched are identically distributed

(actually some small correlation in "model" parameters but will neglect in this course)

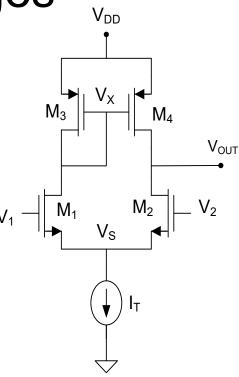

VDD M₄ VOUT  $M_2$  $V_2$ ΙŢ

For each device, the device model is often expressed as

$$I_{Di} = \frac{(\mu_{N} + \mu_{Ri})(C_{OXN} + C_{OXRi})(W_{N} + W_{Ri})}{2(L_{N} + L_{Ri})} (V_{GSi} - (V_{TN} + V_{TRi}))^{2} (1 + (\lambda_{N} + \lambda_{Ri})[V_{DS}])$$

Because of the random components of the parameters in every device, matching from the left-half circuit to the right half-circuit is not perfect

This mismatch introduces an offset voltage which is a random variable

For this 4-transistor op amp, there are 24 uncorrelated random variables

From a straightforward but tedious analysis (involving the 24 random variables) it follows that:

$$\sigma_{V_{OS}}^{2} = 2 \left[ \frac{A_{VTO\,n}^{2} + \frac{\mu}{\mu} \frac{L_{n}}{W_{n}L_{n}} A_{VTO\,p}^{2} + \frac{V_{EB\,n}^{2}}{4} \left( \frac{1}{W_{n}L_{n}} A_{\mu_{n}}^{2} + \frac{1}{W_{p}L_{p}} A_{\mu_{p}}^{2} + A_{COX}^{2} \left[ \frac{1}{W_{n}L_{n}} + \frac{1}{W_{p}L_{p}} \right] \right) \right]$$

where the terms  $A_{VT0}$ ,  $A_{\mu}$ ,  $A_{COX}$ ,  $A_{L}$ , and  $A_{W}$  are process parameters  $V_{DD}$

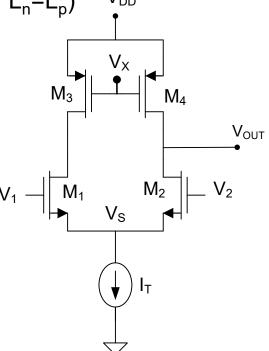

Typical values for matching model parameters:

$$\sqrt{A_{\mu}^{2} + A_{COX}^{2}} \approx \begin{cases} .016\mu \quad (n-ch) \\ .023\mu \quad (p-ch) \end{cases}$$

$V_{1} \longrightarrow M_{2} \longrightarrow M_{2$

(Remember this is due to local random variations)

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO\,n}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTO\,p}^{2} \right]$$

This expression has somewhat peculiar coefficients. The first term on the right is dependent upon the reciprocal of the area of the n-channel device but the corresponding coefficient on the second term on the right appears to depend upon the dimensions of both the n-channel and p-channel devices. But this can be rewritten as

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO n}^{2}}{W_{n} L_{n}} + \left( \frac{V_{EB n}}{V_{EB p}} \right)^{2} \frac{A_{VTO p}^{2}}{W_{p} L_{p}} \right]$$

The dependence of the variance on the area of the n-channel and p-channel devices is more apparent when written in this form.

Correspondingly for differential output structure:

$$\sigma_{V_{OS}}^{2} = 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} + \frac{V_{EBn}^{2}}{4} \left( \frac{1}{W_{n}L_{n}} A_{\mu_{n}}^{2} + \frac{1}{W_{p}L_{p}} A_{\mu_{p}}^{2} + A_{COX}^{2} \left[ \frac{1}{W_{n}L_{n}} + \frac{1}{W_{p}L_{p}} \right] \right) + 2A_{L}^{2} \left[ \frac{1}{W_{n}L_{n}^{2}} + \frac{1}{W_{p}L_{p}^{2}} \right] + A_{w}^{2} \left[ \frac{1}{L_{n}W_{n}^{2}} + \frac{1}{L_{p}W_{p}^{2}} \right] \right) \right]$$

which again simplifies to

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTO n}^{2}}{W_{n} L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n} L_{p}^{2}} A_{VTO p}^{2} \right]$$

Note these offset voltage expressions are identical!

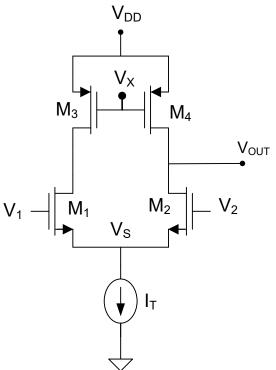

Example: Determine the  $3\sigma$  value of the input offset voltage for The MOS differential amplifier if a) M<sub>1</sub> and M<sub>3</sub> are minimum-sized and

b) the area of  $M_1$  and  $M_3$  are 100 times minimum size (with  $L_n = L_p$ )  $V_{DD}$

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}^{2}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{W_{n}L_{n}} \left[ A_{VTOn}^{2} + \frac{\mu_{p}}{\mu_{n}} A_{VTOp}^{2} \right]$$

a)

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{(0.5\mu)^{2}} \left[ .021^{2} + \frac{1}{3} .025^{2} \right]$$

$$\sigma_{V_{OS}} \cong 72mV$$

$$3 \sigma_{V_{OS}} \cong 216mV$$

Note this is a very large offset voltage !

Example: Determine the  $3\sigma$  value of the input offset voltage for the MOS differential amplifier due to local random variations if: a) M<sub>1</sub> and M<sub>3</sub> are minimum-sized and b) the area of M<sub>1</sub> and M<sub>3</sub> are 100 times minimum size

$$\sigma_{V_{OS}}^{2} \cong 2 \left[ \frac{A_{VTOn}^{2} + \frac{\mu_{p}}{\mu_{n}} \frac{L_{n}}{W_{n}L_{p}} A_{VTOp}^{2}}{W_{n}L_{n}} + \frac{\mu_{p}}{\mu_{n}} \frac{W_{n}L_{p}^{2}}{W_{n}L_{p}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{W_{n}L_{n}} \left[ A_{VTOn}^{2} + \frac{\mu_{p}}{\mu_{n}} A_{VTOp}^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong \frac{2}{100(0.5\mu)^{2}} \left[ .021^{2} + \frac{1}{3}.025^{2} \right]$$

$$\sigma_{V_{OS}}^{2} \cong 7.2 \text{mV}$$

$$3 \sigma_{V_{OS}}^{2} \cong 21.6 \text{mV}$$

Note this is much lower but still a large offset voltage !

The area of  $M_1$  and  $M_3$  need to be very large to achieve a low offset voltage

It can be shown that

$$\sigma_{V_{OS}}^{2} \cong 2V_{t}^{2} \left[ \frac{A_{Jn}^{2}}{A_{En}} + \frac{A_{Jp}^{2}}{A_{Ep}} \right]$$

where very approximately

$$A_{Jn} = A_{Jp} = 0.1 \mu$$

V<sub>CC</sub> Example: Determine the  $3\sigma$  value of the offset voltage of a the bipolar input stage due to local random variations if  $A_{E1} = A_{E3} = 10\mu^2$  $V_{\mathsf{X}}$  $\sigma_{V_{OS}}^2 \cong 2V_t^2 \left| \frac{A_{Jn}^2}{A_{En}} + \frac{A_{Jp}^2}{A_{En}} \right|$  $\sigma_{V_{OS}} \cong \sqrt{2} V_t A_J \frac{\sqrt{2}}{\sqrt{A_r}}$  $\sigma_{V_{OS}} \simeq 2 \bullet 25 \text{mV} \bullet 0.1 \mu \bullet \frac{1}{\sqrt{10\mu^2}} = 1.6 \text{mV}$  $3\sigma_{V_{OS}} \cong 4.7 \text{mV}$

Note this value is much smaller than that for the MOS input structure !

Typical offset voltages:

MOS - 5mV to 50MV BJT - 0.5mV to 5mV

These can be scaled with extreme device dimensions

Often more practical to include offset-compensation circuitry

## Stay Safe and Stay Healthy !

### End of Lecture 22